论文总字数:33338字

目 录

1 绪论 1

1.1 论文研究背景以及意义 1

1.2 论文的研究内容和研究目标 1

2 设计指标以及方案 1

2.1 信号发生器的技术指标 1

2.2 方案论证和设计 2

2.2.1 设计思路 2

2.2.2 方案设计 2

2.2.3 方案确立与系统整体结构体 3

3 设计原理 4

3.1 直接数字频率合成(DDS)的原理 4

3.1.1 DDS简介 4

3.1.2 DDS的基本原理 4

3.2 FPGA简介以及VHDL程序的特点 5

3.3 DDS在FPGA中的实现 5

4 系统硬件设计 6

4.1 FPGA部分设计 6

4.1.1 FPGA类型的选择 6

4.1.2 FPGA对DDS电路的具体实现 6

4.1.3 FPGA对SOPC的接口通信设计 7

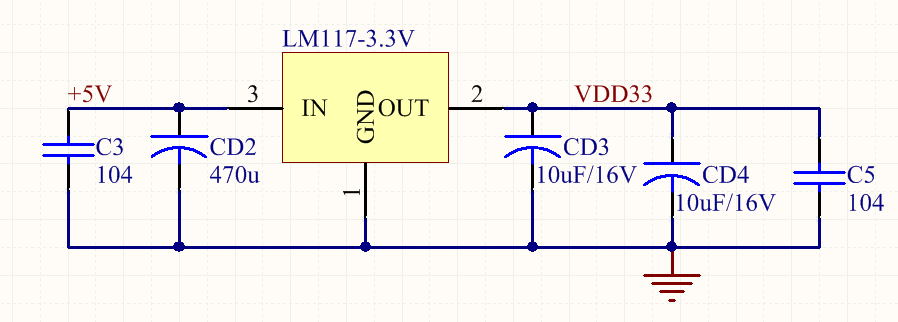

4.2 电源模块设计 7

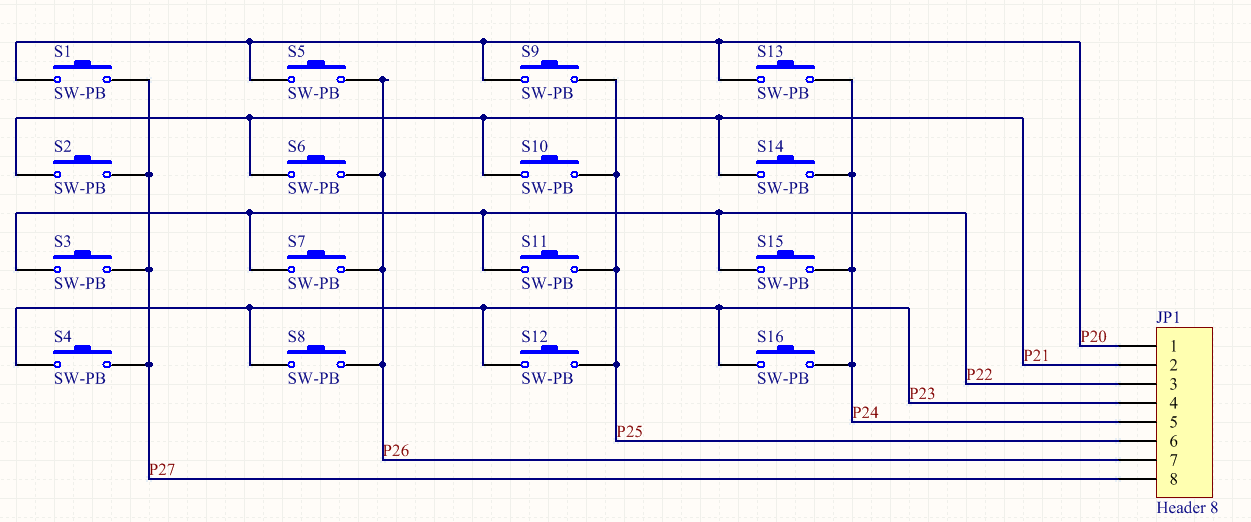

4.3 键盘模块设计 8

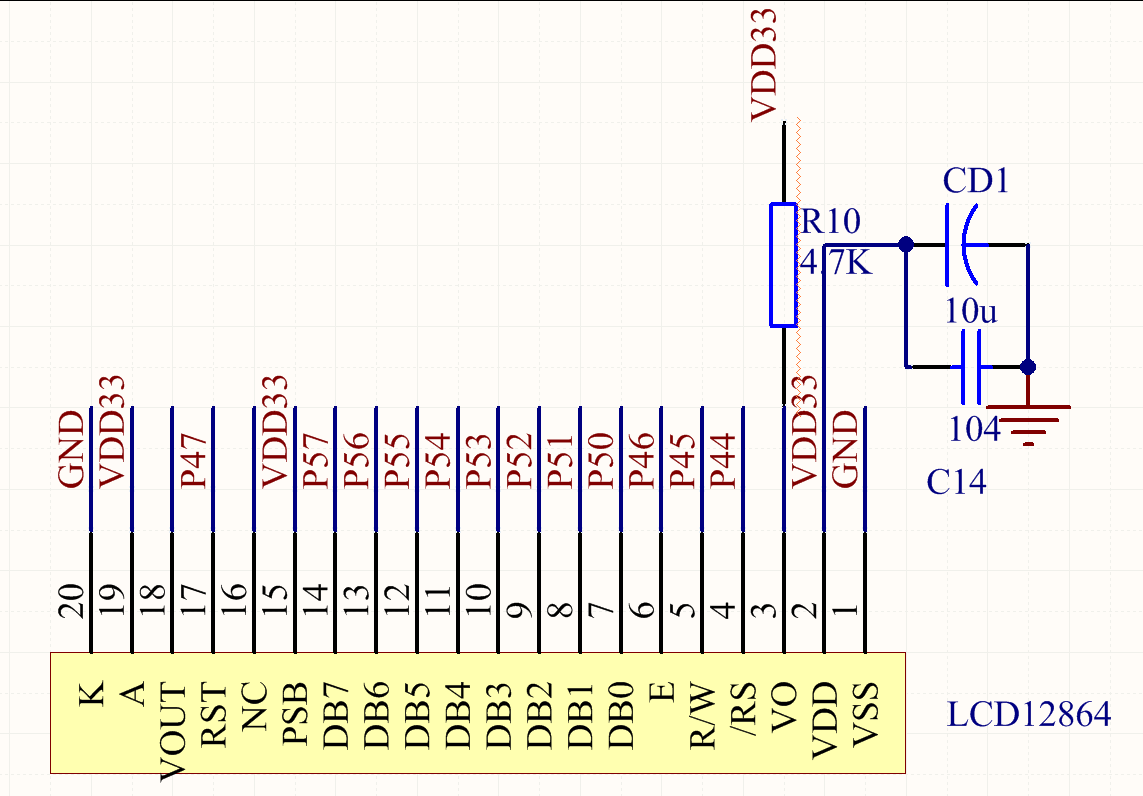

4.4 显示模块设计 9

4.5 D/A转换部分设计 9

4.5.1 DAC0832电路设计 9

4.5.2 DAC5662电路设计 10

4.6 功率放大电路设计 12

4.7 系统PCB设计 12

5 系统软件设计 13

5.1 开发环境介绍 13

5.1.1 QUARTUS II软件介绍 13

5.1.2 NIOS II IDE软件介绍 14

5.1.3 MATLAB软件介绍 14

5.2 FPGA的软件设计 14

5.2.1 系统时钟源的软件设计 14

5.2.2 键盘模块的软件设计 15

5.3 SOPC的软件设计 16

5.3.1 LCD显示模块的软件设计 17

5.3.2 数据处理模块的软件设计 17

5.3.3 EPCS程序存储的软件设计 18

5.3.4 MATLAB查找表设计 18

6 系统调试与测试 20

6.1 系统硬件调试 20

6.2 系统软件调试 20

6.3 系统测试与误差分析 21

7 总结 24

参考文献: 24

致谢 26

附录 27

一种基于FPGA的信号源设计

屈梦祥

, China

Abstract: The design is considered from the reality, in the condition of conventional signal generators having too large volume , and too high price, consuming too much energy, design a compact, stable performance, low-power multi-function signal generator device targeted at laboratory environment. The signal generator can output sine, triangle, square wave three waveforms, amplitude range of 0 to 0 ~ 5V, the frequency range of 1Hz ~ 1MHz. This design uses FPGA technology, uses VHDL language programming to complete, applies the design principles of DDS to achieve DDS functions on FPGA, at the same time, uses SOPC technology control systems on FPGA. This design has a lot of positive significance in teaching and research fields.

Key words: FPGA; Signal generator;DDS;SOPC

1 绪论

1.1 论文研究背景以及意义

信号发生器,也就是我们平时所用到的信号源,在大的范畴理解内,一切能够产生测试信号的仪器都可以称为信号发生器。在本设计的研究预期中,本文提到的信号发生器主要是指在实验室用到的产生不同波形输出的信号源。作为一名电子专业的学生,信号发生器作为重要的信号发生仪器,在我们的学习过程中经常用到。同时,信号发生器也几乎渗透到生活的方方面面,如医疗、教学、生产、科研等,广泛应用于电子电路、系统测试、生活生产等诸多领域。在信号发生器刚出现的时候,几乎全部采用模拟方式,设计电路相对复杂,且频率调节、幅度控制、相位调节都需要进行复杂的电路调节,这些都限制了信号发生的发展。随着科技的进步以及人们对信号发生器性能和功能的要求,信号发生器发展到今天,越来越多的信号发生器已经采用直接数字合成频率技术,即DDS技术,这种技术是以全数字技术从相位出发,直接在一定频率的时钟下准确输出各个相位对应的幅值。因为这种技术产生的波形信号纯度高、相位频率幅值控制方便、转换频率快、分辨率高,很快这种方法设计的信号源便快速发展。

对于电子专业的我们来时,学习并了解信号发生器的原理及设计是我们的必修课之一,而只有在实践中,我们才能不断提高自己的动手能力,才能更深刻的了解信号发生器的工作原理以及设计方法。在FPGA上实现DDS的功能,而不采用DDS芯片,对我们来说可以更好地深入DDS的内部原理,而不是停留在DDS的使用这个表面工作上。在整个设计过程,学生亲自参与,可以了解整个设计原理以及功能拓展方法,这个教学过程中有着极好的引导和学习意义,对于我们自己,可以提高自己的学习能力和动手能力,更好地为自己的发展打下基础。

1.2 论文的研究内容和研究目标

本文的主要研究内容是采用FPGA技术,根据直接数字频率合成技术原理,不采用已有的DDS芯片,而是采用FPGA实现DDS的功能,实现一种体积小、功耗小、精度高、性价比高的实用性信号源。本设计最终输出正弦波、三角波、方波三种波形,实现幅度在0~5V之间可调,频率在1Hz~1MHz之间可调。本文主要从以下几个方面进行论述:

(1)简述信号源的发展及现状,对信号源的设计提出方案和比较

(2)简述DDS的实现原理,以及在FPGA上实现DDS的功能

(3)使用MATLAb软件进行相位取点,生成原始信号的查找表

(4)使用Multisim软件进行模拟电路设计以及相关的仿真

(5)使用Altium Designer软件进行电路原理图的绘制,并制作PCB板

(6)综合整个系统,进行整体系统测试和总结

2 设计指标以及方案

2.1 信号发生器的技术指标

在实际的生产生活中,一个产品生产出来之后,人们关心的是其技术指标是否能够达到预期的要求,对于信号发生器也是如此,本文的信号发生器的主要技术指标包含以下几个方面:

(1)波形种类

波形种类是指信号发生器输出波形信号时的波形的不同形状,本文设计的信号发生器最终输出三种不同形状的波形,分别为正弦波形状信号、三角波形状信号、方波形状信号。

(2)带宽

带宽是指信号发生器输出信号的频率范围,本文设计的信号发生器输出信号频率要求为1Hz~1MHZ。

(3)幅值

幅值是指信号发生器输出信号的最大电压,本文设计的信号发生器输出信号幅值为5V。

(4)频率分辨率

频率分辨率是指信号发生器输出信号时频率的最小可调的取值,即输出波形时波的最小时间间隔,本文设计的信号发生器输出信号的频率分辨率为1Hz。

2.2 方案论证和设计

2.2.1 设计思路

本设计从实际情况出发,主要是在信号发生器的发展下研究和学习其原理以及设计方法,主要针对电子电气、测控、自动化等相关专业的学生,在实验室教学的情况下,与理论相结合,动手设计一款多功能实用的信号发生器,所以最好能够结合相关专业在大学里接受的相关知识,能够较大程度的把学生所学的知识都可以用到设计中来。由此,设计应包含不止是硬件电路,模拟电路等相关知识,还应包含各种软件的使用、程序的编写以及调试。当然,在信号发生器完成后,可以作为平时用的小型信号源,体积不宜过大。在后续的功能拓展,能够方便在原有的基础上进行功能的强化和增加。基于此种设计思路,我们给出了以下的设计方案。

2.2.2 方案设计

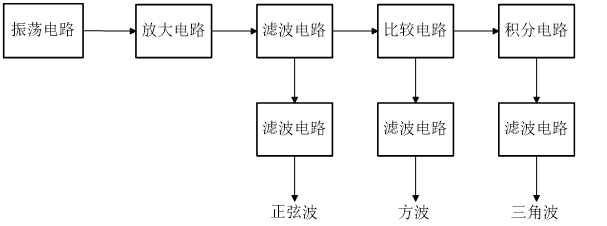

方案一:采用模拟式信号发生器,通过RC振荡电路自己振荡产生原始正弦波,正弦波通过放大器讲幅值放大达到需要的幅度,再经过滤波器,可以直接输出较为纯净的正弦波。正弦波通过一个迟滞比较器,然后将输出电压反馈到比较器的两端,加上限流电阻和两个双向稳压管,组成方波发生电路,从而输出方波。方波经过积分电路对方波进行积分可得到三角波,从而输出三角波。

方案一原理框图如下所示:

图2.1 模拟式信号源原理框图

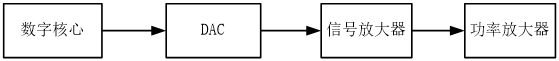

方案二:依托FPGA这个核心平台,实现数字频率合成技术(DDS),在高速时钟信号下, FPGA核心可以查询波形表输出数字式的波形信息,再经过高速DAC产生原始波形,输出几乎无失真的波形。这样输出的信号波形频率范围和幅度范围都较大且可调,同时频率的分辨率也较小。

FPGA核心的主要工作是读取存储在ROM中的波形查找表数据,配合高速时钟采样取点输出波形信息。这样输出的信息为量化的数字信息,需要再经过告诉DAC实现数模转换将数字量转化为模拟量,从而输出原始波形,波形查找表由MATLAB软件直接生成。本设计输出的信号可以通过FPGA核心控制幅度和频率,从而可以实现这三种波形在范围内的任意输出。

原理框图如下所示:

图2.2 数字式信号源原理框图

2.2.3 方案确立与系统整体结构体

通过实践过理论证明,方案一采用模拟电路技术实现信号发生器设计结构复杂,电路设计难度大,抗干扰性差,控制能力差,作为新型的信号发生器已经很难做到满足我们的需求。

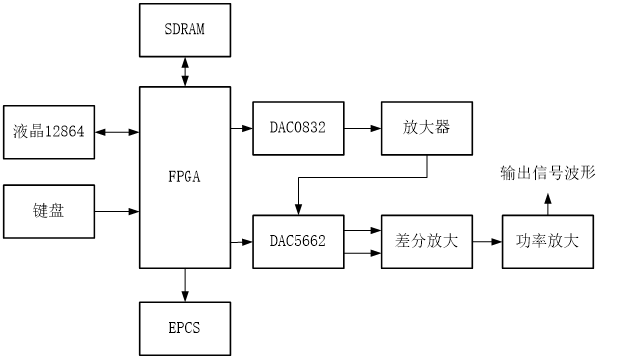

相对来说,方案二的数字式信号发生器的设计较为可行,在FPGA的平台上应用直接数字频率合成技术的原理实现DDS的功能,方便对输出的波形信息进行控制、修改、以及存储。而方案二所论述的系统也涵盖了在大学期间我们所学的知识,不仅包含了硬件电路如电源模块、D/A转换模块等,而且包含软件编程部分,如FPGA在PLL中实现三路倍频、分频等。更好地贴切了我们的设计思路,有助于学生强化学习过的理论知识、培养学生的钻研精神、提升自身综合能力等,所以我们选择方案二。在本设计方案中,我们不再外接单片机控制系统,而是使用FPGA本身可利用的SOPC作为信号发生器的控制核心,达到节省资源的目的,同时使系统更加优化与稳定。为了更好的实现本设计的功能,使用户友好度更高,我们另外增加了矩阵键盘模块和LCD12864显示模块,键盘模块用来修改输出波形的信息,LCD12864显示模块用来显示波形信息如波形种类、幅度、频率等。

整个系统的组成框图如下图所示:

剩余内容已隐藏,请支付后下载全文,论文总字数:33338字

相关图片展示:

该课题毕业论文、开题报告、外文翻译、程序设计、图纸设计等资料可联系客服协助查找;