论文总字数:29369字

摘 要

全球定位系统(Global Positioning System,GPS)经过三十余年的研究与发展,已成为世界范围内使用范围最广的卫星导航定位系统,深刻影响着军事和民用的各个领域。而随着设计方法的改进以及制造工艺的发展,GPS基带电路的集成度和集成密度不断提高,功耗问题已经越来越引起设计者的关注。功耗的增加会影响集成电路的性能和可靠性,同时也限制了集成电路的运用范围。低功耗设计逐渐成为GPS基带电路设计中一个不可回避的课题。

低功耗的设计思想可以运用到集成电路设计的各个阶段,本文重点研究了GPS基带电路的RTL级低功耗优化。首先研究了集成电路低功耗技术研究现状以及GPS基带电路的低功耗研究的发展历程,分析了CMOS电路功耗的主要来源是动态功耗,介绍了一些常见的RTL级低功耗设计方法。其次,介绍了GPS基带电路的整体构架,重点分析了跟踪部分的累加器、状态机以及捕获部分的匹配滤波器、多普勒鉴频模块,给出了相应的优化方案,并且运用了门控时钟。论文最后给出了一个基于VCS验证环境、Design Compiler综合环境和PrimeTime PX功耗分析环境的优化流程,并且给出了基于此流程的实验结果和分析。

RTL级低功耗优化需要在功耗、面积以及性能三个方面做出权衡。实验结果证明合适的算法改进和电路结构的变化可以在不影响电路性能的情况下,降低电路的动态功耗。

关键词:RTL,低功耗,GPS,累加器,格雷码,匹配滤波器,门控时钟

Abstract

Global Positioning System (GPS) has become the world's most widely used satellite navigation and positioning system after more than 30 years’ research and development, deeply influencing the military and civilian fields. With the improvement of design method and the development of manufacturing technology, the GPS baseband integrated circuit increases its integration density, and power consumption problem has increasingly aroused the concern of designers. Increased power consumption will affect the performance and reliability of integrated circuit and at the same time also limits the application range of the integrated circuit. Low-power design has gradually become an unavoidable topic during the GPS baseband circuit design.

Low-power design can be applied to all stages of integrated circuit design, this paper mainly studies GPS baseband circuit low-power optimization in the register transfer level (RTL). First, this paper studies the current research situation of low-power integrated circuit and the research of low-power GPS baseband circuit development, analyzes that the main source of CMOS circuits power consumption is dynamic power, and introduces some common methods of RTL low-power design. Secondly, this paper introduces the overall framework of GPS baseband circuit, analyses accumulator and state machine in the tracking module as well as matched filter and Doppler frequency module in the acquisition module, presents a corresponding optimization scheme,and applies clocking gating. Finally, this paper gives a total optimization process based on VCS verification environment, Design Compiler synthesis environment and PrimeTime PX power analysis environment, and the experimental results based on the process are given and analyzed.

The RTL low-power optimization should weigh and balance between three aspects including area, power consumption and performance. Experimental results show that appropriate algorithm and circuit structure changes can reduce dynamic power consumption of the circuit under the condition of not affecting the circuit performance.

Key Words: RTL, low-power, GPS, accumulator, grey code, matched filter, clock gating

目 录

摘 要 I

Abstract II

目 录 III

第一章 绪 论 1

1.1. 论文的背景 1

1.1.1 低功耗技术研究现状 1

1.1.2 GPS低功耗研究现状 2

1.2. 论文的主要工作和意义 2

1.3. 论文的结构 3

第二章 RTL低功耗技术分析 4

2.1. CMOS电路的功耗来源 4

2.2. 各设计层次的低功耗技术 6

2.3. RTL级低功耗优化技术 7

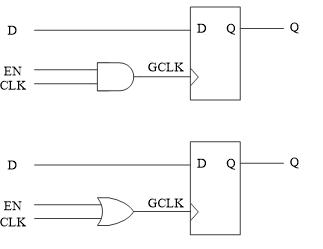

2.3.1 门控时钟 7

2.3.2 逻辑重组 9

2.3.3 预计算 10

2.3.4 操作隔离 11

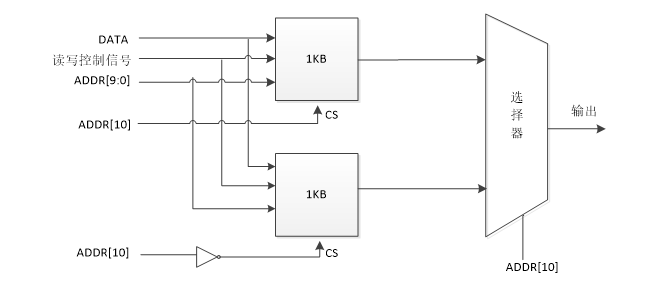

2.3.5 存储器分块访问 12

第三章 GPS的结构及优化 13

3.1. GPS接收机的组成及定位原理 13

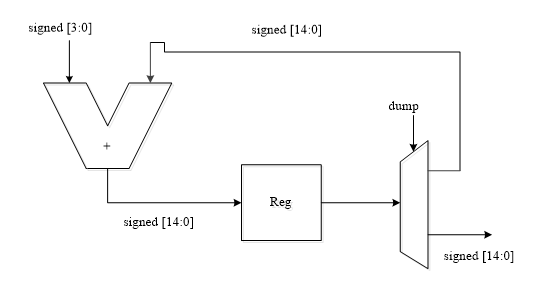

3.2. 跟踪部分相关器的优化 14

3.2.1 累加器的工作特点 14

3.2.2 基于计数器的累加器 15

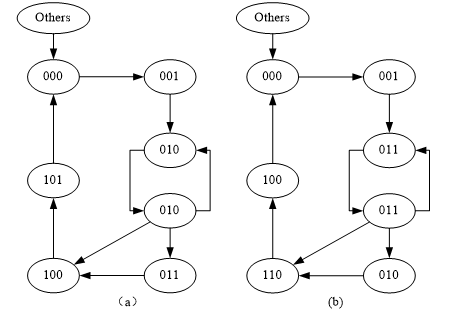

3.3. C/A码产生过程中状态机的优化 16

3.4. 匹配滤波器中加法器的优化 16

3.4.1 数字匹配滤波器的功能及初始结构 16

3.4.2 分级加法器 17

3.4.3 基于全加器的冗余二进制编码加法器 18

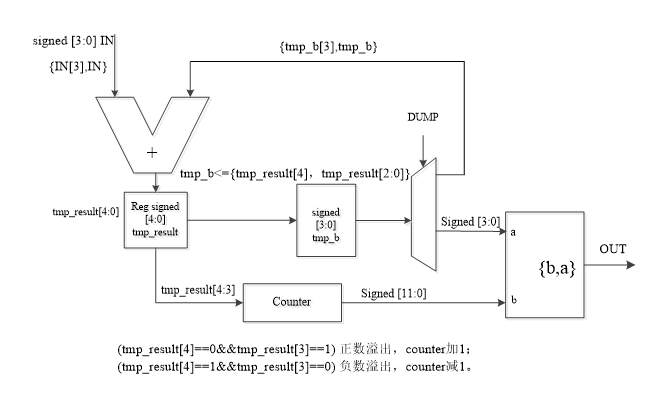

3.5. 鉴频模块的优化 20

3.5.1 频率并行搜索的原理 20

3.5.2 优化方案 20

3.6. 门控时钟的使用 21

第四章 功耗优化流程和结果分析 22

4.1. 低功耗优化及测试流程 22

4.1.1 功能验证 23

4.1.2 逻辑综合 24

4.1.3 门级仿真 25

4.1.4 功耗评估 25

4.2. 优化结果 26

4.2.1 跟踪部分累加器的优化结果 26

4.2.2 状态机的优化结果 27

4.2.3 门控时钟的优化结果 27

4.2.4 匹配滤波器的优化结果 28

第五章 总结与展望 29

致谢 30

参考文献 31

第一章 绪 论

论文的背景

全球定位系统(Global Positioning System,GPS),是美国在20世纪70年代开始研制的卫星导航系统,由空间星座部分、地面监控部分和用户设备部分等三个独立的部分组成[1]。空间星座部分由多颗GPS卫星组成,可以向地面发射卫星信号,地面监测部分可以接收卫星信号,这两者为GPS提供了定位基础。用户设备部分主要由导航数据处理软件和接收机硬件组成,用户通过GPS用户设备实现定位。GPS能够提供高精度的时空标注和全天候、全球性的导航服务。

GPS的发展过程可分为三个阶段。1978年到1979年为第一阶段,这一阶段主要研制了地面接收机,建立了地面跟踪网。1979年到1984年为第二阶段,这一阶段发射了7颗试验卫星,研究制造了各种用途的接收机。1984年之后为第三阶段,这一阶段进行了GPS系统工程建设,即GPS卫星星座的布局设置。1995年,GPS正式进入全面运行阶段。

GPS最初是为了满足军事领域在海、陆、空三个层面对定位、授时和通信的需求,近年来,GPS在民用领域的运用得到了飞速的发展。比如,海面上的船舶导航、进港引水,地面上的汽车自主导航、城市智能交通管理系统、网络系统的授时与校频、工程测量、资源勘查,空中的飞机航路引导、进场降落引导等。GPS与电子地图相结合,使得个人的终端设备功能更加齐全,包括手机、平板电脑、相机、运动设备等,给人们的生活与工作带来了极大的便利。

用户设备部分是GPS三个组成部分中最有发展前景的一部分,主要由射频前端处理电路、基带信号处理电路、方位解算三个部分组成。传统的GPS基带信号处理电路往往将电路的处理速度及芯片的面积放在设计的首位,很少将电路的功耗列入设计的考虑范围。但是,随着集成电路的工艺水平向深亚微米发展,电路的集成度越来越高,电路的单位面积功耗和整体功耗也随之增长,而功耗的增长在很大程度上会影响电路性能的可靠性。此外,移动设备的电池寿命是一定的,这一因素也制约着移动设备的发展。因此,GPS基带信号处理电路设计者们必须将低功耗列这一重要课题列入考虑范围,在处理速度、面积、功耗三者之间对芯片的整体性能进行评估。

1.1.1 低功耗技术研究现状

目前,低功耗优化技术分布于电路的系统级、算法级、寄存器传输级(Register Transfer Level,RTL)、门级(又称晶体管级)、版图级和工艺级等各个层次。这些技术大多数已经非常成熟,并且在大规模集成电路中得到应用,取得了较好的效果。其中,RTL级是电路逻辑设计的起点,也可以是电路低功耗设计的起点[2]。常用的RTL级低功耗优化技术包括逻辑重组、预计算、操作隔离、门控时钟、存储器分块访问、状态机优化和总线编码等。此外,已经有RTL级的EDA优化工具投入使用,包括Spyglass、PowerPro、PowerArtist等。

PowerPro RTL工具是Calypto公司开发的RTL级低功耗优化工具。它有精确的翻转活动传播,包括时序翻转活动,能够通过时钟门(PowerPro CG)和内存门(PowerPro MG)进行自动功率优化处理。采用常见的RTL优化方法,一般可以在RTL级降低9%到12%的功耗。但有一个缺点是目前还不支持统一功率格式(UPF,Unified Power Format)和通用功率格式(CPF,Common Power Format)。UPF将在1.1.2节作详细介绍。

PowerArtist工具属于Apache/Ansys公司,它内嵌时序敏感算法,能够在RTL级和门级预测整体SoC的功耗情况,支持精细的功耗优化技术,比如门控电源、多电压域、多阀值电压等,消除了RTL、门级网表和物理网表之间不必要的迭代。设计者可以把精力放在最大的功耗节省机会上,从而达到尽可能少的修改RTL,同时获得尽可能多的功耗降低。PowerArtist可以降低3% 到10% 的功耗,可以读入UPF或CPF。但是,并没有正式的验证方法比较原始的RTL文件与PowerArtist产生的新RTL文件,使用者只能通过功能仿真验证新RTL文件的功能正确性。

SpyGlass工具是Atrenta公司的RTL级低功耗优化工具,针对VERILOG和VHDL用先进的静态和动态分析在RTL层面上预估芯片性能、分析功耗效率问题,支持门控时钟、状态及优化、预计算、操作隔离等多种技术,从而引导设计人员在还没有达到后端工序的情况下快速地进行功耗的优化,开发出更加优化的RTL代码。与前两个工具不同之处在于它通过UPF或CPF考虑了电路的功耗设计意图,并且能够正式地对输入的原始RTL和输出的优化过的RTL进行时序等价检查。通常,可以降低9% 到16%的功耗,是三个工具中最高的一个。

1.1.2 GPS低功耗研究现状

目前,实验室的GPS课题组已经采用Synopsys UPF的办法降低了GPS基带信号处理电路的功耗。由于HDL不支持对电源连接的描述,因此UPF就是对RTL的扩展,以仿真门控电源的工作。UPF文件是一组TCL命令,是一个被广泛采用、互操作性强的低功耗实现标准,能够贯穿于功能仿真、逻辑综合、物理实现等整个IC设计实现验证流程。UPF文件中最主要的就是电源关断单元(Power Gating)。Power Gating可以控制静态功耗,实质就是在系统运行期间,若发现系统的某个电路块在一段时间内闲置,没有实际的动作,则在这段空闲时间内把供电电源切断,那么电源关断区域的漏电流几乎可以减小到零,这极大程度地减小了电路的静态功耗。

此外,还采用了门控时钟、操作隔离等技术对RTL代码进行优化,进一步降低了电路的功耗。门控时钟和操作隔离这两种技术将在2.3节作详细介绍。

论文的主要工作和意义

实验室已经完成了基于Verilog HDL设计的GPS基带信号处理电路的设计,经过仿真软件VCS的功能验证以及FPGA的性能验证,能够很好地满足预期的性能要求。

剩余内容已隐藏,请支付后下载全文,论文总字数:29369字

相关图片展示:

该课题毕业论文、开题报告、外文翻译、程序设计、图纸设计等资料可联系客服协助查找;