论文总字数:25970字

摘 要

在嵌入式CPU/SoC中,静态随机存取存储器SRAM所占的比重逐渐增大;并且,系统对SRAM性能的要求越来越高;随着工艺节点向深亚微米级的特征尺寸推进,先进工艺技术使设计规则越来越复杂、掩膜成本越来越高。为了在高度竞争的市场中能够快速地获得存储器,并且最大限度地控制开发周期和成本投入,需要一种高效率的半定制SRAM设计方法。SRAM编译器技术就能够满足这一要求,它能够快速、高效、低成本地自动生成不同容量的SRAM IP核。

在SRAM编译器算法中,版图和网表拼接算法是重要算法之一,该算法的基本思路是:按照一定的布局和层次结构,由底层单元拼接出上层单元,直至拼接出SRAM整体电路的版图和网表。网表拼接主要关注单元间端口的连接关系;版图拼接主要关注单元放置的位置,本文中重点研究了基于交叠距离的版图拼接算法和版图定点编程单元拼接算法。

本文实现了版图和网表的拼接脚本,利用SRAM版图和网表编译器,完成了字数为64-8192、字长为4-128的SRAM电路整体版图和网表的拼接,并在Cadence平台对版图和网表进行了DRC和LVS验证。

关键词:SRAM,编译器,拼接算法

Abstract

The proportion of SRAM in embedded CPU/SoC is going to remain increasing gradually. At the same time, the requirement for SRAM performance is also increasing. In addition, as the technology is scaling down to deep submicron, the complication of design rules and cost of mask, which are brought by advanced technology, are getting worse. To get memory quickly in the highly competitive market and control cycle time and cost of manufacture, an effective self-custom SRAM design method is needed. SRAM compiler can meet the requirement perfectly for that compiler can generate SRAM IP core quickly, effectively and economically.

The tiling algorithm of layout and netlist is one of key algorithms in SRAM compiler. The basic thought of this algorithm is bottom-up method. In according to stated topology and hierarchical structure, lower level modules are tiled to form upper level module. And this procedure is repeated until the top level module is developed. The tiling of layout concerns about the coordinates of modules mostly, so this paper discusses a tiling algorithm of layout based on the overlap distance and a fixed point programming tiling algorithm of layout. However, the tiling of netlist concerns the connection of adjacent modules’ ports.

This paper develops layouts and netlists of SRAM overall circuit, from 64 words up to 8192 words and from 4 bits up to 128 bits, by editing tiling script files and layout and netlist compiler. And we conduct DRC and LVS verification to the automatically generated layouts and netlists on Cadence.

Keywords: SRAM, compiler, tiling algorithm

目录

摘要 I

Abstract II

目录 III

第一章 绪论 1

1.1 存储器简介 1

1.2 SRAM编译器 2

1.3 拼接算法概述 3

1.4 主要工作 3

1.5 论文结构 3

第二章 SRAM基本结构和工作原理 5

2.1 SRAM基本结构 5

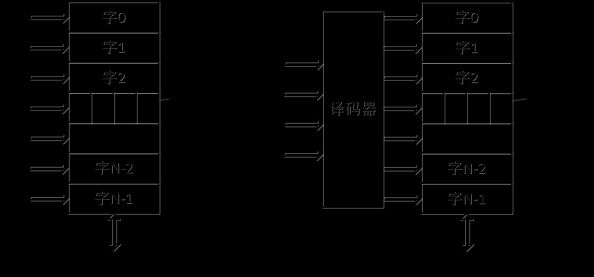

2.1.1 存储阵列 5

2.1.2 存储单元 7

2.1.3 地址译码器 8

2.1.4 灵敏放大器 9

2.2 SRAM工作原理 11

2.2.1 读操作 11

2.2.2 写操作 12

2.2.3 数据保持 12

第三章 SRAM编译器中的拼接技术 13

3.1 拼接脚本 13

3.2 版图拼接算法 13

3.2.1 版图拼接算法描述方式 14

3.2.2 基于交叠距离的版图拼接算法 15

3.2.3 版图定点编程单元添加算法 16

3.3 网表拼接算法 17

第四章 版图、网表的拼接及验证 20

4.1 版图拼接 20

4.2 网表拼接 25

4.3 编译器生成的版图与网表验证 25

第五章 总结 30

致谢 31

参考文献 32

第一章 绪论

1.1 存储器简介

存储器是数字系统的重要组成之一,广泛应用于电子通信、航天、国防等各领域。在SoC(System on Chip)设计中,设计者将存储器嵌入到电路中,以此来提高系统的效率,并减少电源功耗和封装成本。根据SIA(Semiconductor Industry Association)的统计,集成电路的发展使单芯片上能够集成的存储器数量逐渐增大;另外,存储器面积在芯片上的比例也逐渐增加。这些事实显示存储器在SoC中逐渐占据支配地位。

半导体存储器是一种重要的存储器,起源于20世纪60年代。在当今的SoC芯片中,存储器中的晶体管比例达到70%以上,而且在可预见的未来,这个比例将继续增加;在计算机中,半导体存储器容量可达10G字节以上,并且随着集成电路技术发展,这一数字也在持续增长。因此,半导体存储器是数字逻辑系统设计中最重要的微电子器件。得益于工艺水平的进步,半导体存储器的存储容量增大,性能也得到提升,从而使数字逻辑系统的性能受到很大的有利影响。

存储器产品种类众多,往往采用最先进的半导体工艺,是集成电路技术发展水平的代表,其研究和生产水平向来是衡量一个国家科技和工业发达程度的标志。当前,各种存储器的产量和市场占有率的次序为DRAM(Dynamic Random Access Memory)、SRAM(Static Random Access Memory)、ROM、EPROM、E2PROM和Flash。其中,SRAM即静态随机存取存储器,是一种由CMOS基本单元构成的存储器。基于正反馈原理,交叉耦合的反相器构成与锁存器类似的双稳态结构,实现SRAM内部数据的保存。在无操作时,“锁存器”处于稳态,数据稳定,不需要周期性地进行电荷刷新,速度很快。在断电后,SRAM所存储的数据丢失;由于所存数据的完整性需要由连续供电来维持,因此SRAM是一种易失性存储器。

与DRAM即动态随机存储器相比,SRAM的存取速度更高,功耗更低[1-2]。因此目前在SoC片上存储器中,SRAM仍将占据主导地位。

随着SoC的发展及应用复杂度的不断提升,SRAM容量及占整个芯片面积的比例越来越大,如图1-1所示,SRAM已占据整个芯片的大部分延时和功耗,在数字系统关键路径上的SRAM已成为制约系统性能的瓶颈。因此,SRAM的研究变得越来越重要。

图1-1 SoC中SRAM的面积与功耗比例趋势图

1.2 SRAM编译器

如今市场应用复杂度不断提升,系统对SRAM性能的要求越来越高;另外,随着工艺节点向深亚微米级的特征尺寸推进,设计规则越来越复杂,掩膜成本越来越高。为了在高度竞争的市场中能够快速地获得存储器,并且最大限度地控制开发周期和成本,需要一种高效的半定制SRAM设计方法。

目前,SRAM设计有两种方法:一种是全定制设计,按照用户的需求进行量身定做,手工设计、拼接SRAM的架构和电路模块,可以优化每个器件的电路参数和版图参数,能灵活地适应体系的各种要求。第二种方法是编译器(Compiler)技术,根据用户需求自动产生SRAM IP核:采用预先设计好的基本单元库中的SRAM单元电路,根据用户输入的指标(字数、字宽、列复用数、是否支持位写等),自动完成SRAM版图的拼接,并自动生成网表和各种仿真模型。

全定制设计的周期通常为3-6月,所需人力大,适应性差,未来的扩展成本高,资源复用性差,一旦设计反复,更是需要投入成倍的成本[3],尤其是随着SRAM容量不断增大、工艺尺寸不断缩小,SRAM的设计对于芯片良率的影响越来越敏感。这时,采用SRAM编译器就可以有效解决设计效率问题。

利用编译器来设计SRAM,一方面由全定制设计的基本单元电路来保证高性能;另一方面,编译器自动生成SRAM IP,并生成GDSⅡ版图、SPICE网表、LEF文件、时序和功耗文件、Verilog模型和用户手册等六种文件,整个过程在数分钟甚至数秒内就能完成。目前,市场要求的上市时间越来越短,芯片设计人员为了提高效率、降低成本,逐渐偏向于使用SRAM编译器来快速生成不同容量的SRAM IP,而生成的IP核可以直接嵌入到芯片系统中进行系统仿真,设计效率得到大大提高。

单个处理器芯片中使用的SRAM存储器数目逐渐增多,而且在同一个设计中需要各种容量不同或结构不同的SRAM存储体(如Cache、TLB、FIFO等),如果完全用全定制方法来设计这些存储器就会十分困难,因此利用编译器技术来生成SRAM的要求日益迫切。

近年来,很多集成电路设计公司致力于开发存储器编译器,如IPCore、VeriSilicon、Artisan、Faraday等公司研发的用于商业目的的存储器IPs。另外,SRAM IP对于现代晶圆厂来说也十分重要,它不仅是晶圆厂技术成熟度的标志,而且是SoC客户最重要的IP之一。很多芯片制造厂也有存储器编译器,如TSMC、SMIC、UMC等向客户提供的多种存储器IPs。

当前已有的编译器设计方法主要有以下两种:

方法一:结合第三方工具的使用来开发编译器,如Synopsys公司的MemoryBuilder、Interra System公司的MC2工具等,用户通过工具中的选项来配置自己所需的存储器单元模块版图,由工具来抽取用于LVS(Layout Versus Schematic)及功能验证的网表,再产生时序信息,最终实现编译器的整个流程。这种方法简化了编译器的开发过程,通过第三方工具来完成大量如建立基本单元库、时序模型等工作;但是这种方法严重依赖于第三方工具授权,带来了高成本的缺点。

方法二:由设计者人工建立基本单元库、产生相关模板文件,并选择EDA工具所提供的专用编程语言作为编译器的实现语言,如Cadence的Skill语言、Compass设计系统的Slice语言等。这种方法基于Cadence等相应工作平台,不需要解析GDS等格式的文件,实现方便,开发难度较小;但依赖于工作平台,可移植性较差。

1.3 拼接算法概述

版图和网表拼接算法是SRAM编译器的重要算法之一。

从20世纪80年代起,国际上就开始进行版图编译器的研究,虽然各个研发团队的版图编译器的电路种类、结构和功能有所差别,但基本设计思路相近:调用预先设计的基本单元版图,按照一定布局和层次结构,自底向上,由底层单元拼接出上层单元,直至拼接出电路的整体版图。在版图拼接中,程序算法的处理对象主要有:单元的版图、单元的版图端口、子单元在上层单元中的例元等,处理动作是以对准物做为基准,对单元版图执行对齐、拼合、连线等操作,以形成上层单元。

现有版图拼接算法是基于pitch-match方法的,在拼接中,模块的边角对齐表示模块间的端口连接在一起。对于具有交叠区域、需要源漏共用的模块,必须重新定义一个空白模块,其大小与交叠区域相等,然后分别与两侧模块的边角对齐,实现具有交叠区域的两个模块的拼接[4]。由于pitch-match方法需要定义许多额外的空单元,拼接脚本的复杂度高,而且编译器的速度会受到影响。为了提高版图拼接的效率,本文采用一种基于交叠距离的版图拼接算法,用来处理交叠或不交叠的版图单元放置问题。

另外,在版图拼接中,根据不同的容量配置,有一些变化的单元需要改变连接关系,典型的例子是行译码器中变化的连线单元。因此,为了实现不同的连线方式,需要在连线部分的某些特定位置进行自由编程并添加单元。

与版图拼接算法类似,网表拼接算法的基本设计思路为:调用预先设计的基本单元网表,按照电路层次结构,自底向上,由小单元拼接出大单元,直至拼接出电路的整体网表。在网表拼接中,程序算法处理的对象是各单元之间的接口对应的连接关系,不需要考虑单元间的位置关系,因此可以认为所有的网表子模块都是无尺寸的。在拼接网表时,需要清楚地描述外部信号端口以及在各模块之间的所有连接信号线。

1.4 主要工作

本文主要研究了作为SRAM编译器中重要算法之一的版图和网表拼接算法,重点是版图拼接中的基于交叠距离的拼接算法和版图定点编程单元添加算法,即不按照边角对齐来拼接版图,而是按照交叠距离来对齐;对于随容量变化的单元,在特定位置进行自由编程并添加单元。

基于定制SRAM,划分SRAM的基本模块和单元,并建立版图和网表基本单元库。利用SRAM版图和网表编译器,编写拼接脚本,自动生成字数为64-8192、字长为4-128的SRAM版图和网表,并进行DRC(Design Rule Check)和LVS验证。

1.5 论文结构

本文的组织结构如下:

剩余内容已隐藏,请支付后下载全文,论文总字数:25970字

相关图片展示:

该课题毕业论文、开题报告、外文翻译、程序设计、图纸设计等资料可联系客服协助查找;