论文总字数:27118字

摘 要

本科生签名: 指导导师签名: 日期:

连续时间∑-∆调制器反馈DAC的设计

摘 要

本文用自行设计的连续时间∑-∆调制器中的反馈数模转换器(DAC)及其校准电路,研究了整个∑-∆调制器中反馈通道的非线性因素的影响以及针对其的校准方法。

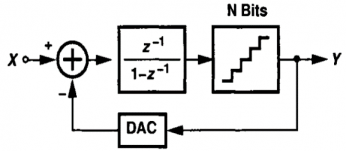

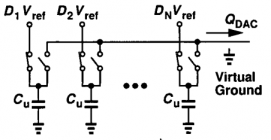

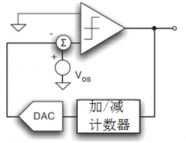

介绍了∑-∆模数转换器(ADC)的原理、结构以及对调制器中重要的性能参数进行了研究以及分析。通过对∑-∆ADC的结构的介绍引出其中反馈回路的DAC,进而对其在整个ADC中的工作状况及存在的非线性问题进行分析。借用数字校准的方法来研究对反馈DAC的校准问题,对三种动态匹配技术:传统DEM、ILA以及DWA算法,通过Matlab进行了建模以及仿真,根据具体需要,最终确定传统DEM算法的电路设计。最后通过cadence软件对所设计的带有DEM校准模块的反馈DAC进行电路实现,并将整个校准后的反馈DAC加入到∑-∆调制器中,通过spectre 对其进行系统仿真。通过建模与仿真探索使用动态匹配算法的优缺点,分析使用该算法前后整个调制器信噪比的变化情况,进而判断校准技术的有效性。

关键词:∑-∆调制器,反馈DAC,数字校准,动态匹配

A DESIGN OF THE FEEDBACK DAC IN THE

CONTINUOUS TIME ∑-∆ MODULATOR

Abstract

In this thesis, it presented a self-designed feedback digital analog converter(DAC) of the continuous time ∑-∆ modulator and its calibration circuit. The nonlinear factors and its calibration methods for the whole ∑-∆ modulator in the feedback channel were discussed.

Principles, structures and important performance parameters of the ∑-∆ analog digital converter(ADC) modulator were studied and analyzed. The DAC in the feedback was introduced by presenting the structures of the ∑-∆ ADC, and then the working conditions of the whole ADC as well as the nonlinearities were discussed. It searched the correction matter by looking into the Digital calibration algorithms. Studied the algorithms of traditional DEM, ILA and DWA, modeling and simulation in the Matlab and chose the DEM algorithm. At last, it put the DAC circuit using the calibration module that used the DEM algorithm into reality by using the cadence software. The whole calibrated feedback DAC was put into the modulator and simulated by the spectre. By simulation compared the advantages and disadvantages of the DEM algorithm, analyzed the changes of the SNR and judged the availabilities of this Digital calibration algorithm.

KEY WORDS:∑-∆ modulator,feedback DAC,Digital calibration,DEM

目录

第一章 绪论 - 1 -

1.1 课题来源及研究的目的及意义 - 1 -

1.2 研究发展状况 - 1 -

1.3 本文内容以及主要的研究工作 - 2 -

第二章 ∑-∆模数转换器原理及结构 - 3 -

2.1 Σ-∆模数转换器的基本概念及工作原理 - 3 -

2.1.1 量化噪声 - 3 -

2.1.2 过采样率 - 4 -

2.1.3 信噪比 - 4 -

2.2 Σ-∆模数转换器的结构 - 5 -

2.2.1 单环高阶Σ-∆调制器 - 5 -

2.2.2 多位量化器 - 7 -

2.2.3 数模转换器DAC - 7 -

2.3 小结 - 9 -

第三章 反馈DAC的线性化 - 10 -

3.1 DAC的主要性能参数 - 10 -

3.1.1 静态性能参数 - 10 -

3.1.2 动态性能参数 - 11 -

3.2 Σ-∆调制器中有关反馈DAC的问题 - 12 -

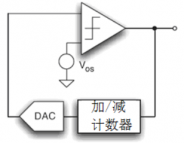

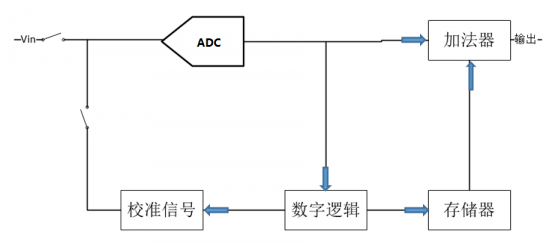

3.3 数字校准技术简介 - 13 -

3.4 数字校准技术的研究方法 - 14 -

3.4.1 元件的修正 - 14 -

3.4.2 前台校准 - 15 -

3.4.3 后台校准 - 16 -

3.4.4 动态匹配 - 17 -

3.5动态匹配技术的实现及Matlab仿真 - 21 -

3.5.1 传统动态匹配技术的建模与仿真 - 21 -

3.5.2 个体层面的平均技术的建模 - 25 -

3.5.2 数据加权平均技术的建模 - 26 -

第四章 ∑-∆调制器DAC反馈的系统设计 - 27 -

4.1 整体结构设计 - 27 -

4.2 反馈电流源DAC电路设计 - 27 -

4.3 随机序列产生电路 - 29 -

4.4反馈DAC电路的仿真及结果分析 - 30 -

4.5 本章小结 - 31 -

第五章 总结与展望 - 32 -

参考文献 - 33 -

致谢 - 35 -

绪论

课题来源及研究的目的及意义

随着现代通信系统的发展,模拟和数字电路的设计面临着越来越巨大的挑战。而数模转换器/模数转换器被认为是系统中面临挑战的核心部分之一。新的通信系统要求数据转换器形成一个新的规范。对于处在接收机的输出端后面的模数转换器则被给予更高的要求。在近期的技术中,由于各种操作的速度越来越快,因此模拟电路的设计面临空前挑战。数字校准需要变得更加复杂才能实现对模拟电路中非理想因素的校准。除此之外,IC技术中越来越低的工作电压也是一个减少特征尺寸的原因。

过采样模数转换器已经成为高位数(16位或更高)电路的最多选择。通常情况下,过采样模数转换器通过高过采样率来将信号频带中的信号数字化来实现,而在这样的技术中,采样频率受限制也是可能的。

Sigma-delta(ΣΔ)调制器被广泛地认为是一种实现高频和超高频A/D和D/A转换器的经过验证了的技术。传统的实施方案是使用原本就是线性的单位数字转换器,通过这种方法借此来实现所需要的指标以及达到所需要的性能。当然,除了单位数字转换器,使用多位数字转换器则可以得到更高的性能。虽然这种方案拥有众多的优势,但是这些优势之中有一个十分重要的问题影响整体性能。该问题在于如何减少滤波设备并且减少整体对调制器的不稳定性的敏感度,从而得到一个更加优越的噪声整形并减少对时钟抖动的敏感度。

因此这种多位调制器需要一个高效的、线性的并且有较好的低噪声性能的数模转换器(DAC)。这已经成为研究动态器件匹配技术的驱动力。通过前人研究的这些技术,使得实现一个线性的多位数模转换器成为可能。尽管DAC经常产生一系列的不匹配噪声,但是这种附加产生的噪声可以通过其他方式被整形。在一个全面的理论研究中,多位数模转换器可以通过其他方式提高线性度已经被验证。同时,许多为动态器件匹配发明的实用技术也被展现在世人面前。

研究发展状况

Σ-Δ调制技术从开始应用到今天,大约有60年的历史了[1]。它是由Inose等人在1962年首次提出于的[2]。当时这些人在一个模数转换系统中采用了这种技术,最终实现了5KHz的信号带宽,并且达到了40dB的信噪比。Ritchie在1974年提出了一种高阶环路滤波的理论[3],之后在1986年,由Adams等人将这个理论应用于实际,实现并完成了一个18bit的ADC[4]。由于Σ-Δ模数转换器相比其他结构有很一定的优势,一些 MASH结构的调制器、数字方法纠正技术以及失配误差整形算法相继被提出,而后人针对各自的特征又进行了相应的优化。从2007年以后,探索者的方向就开始转向了对DAC动态误差的校正,并由此产生了树形结构以及附加延时电路等方法[5][6]。目前,Σ-Δ模数转换器已经基本可以满足低过采样率、功耗小、传输速度快等要求。

1.3 本文内容以及主要的研究工作

本文的研究主要是针对连续时间∑-∆调制器中的反馈DAC的非线性性进行数字校准。为了降低由器件的失配引起的误差,研究了几种数字校准的方法,详细的研究工作大致分为以下几个方面:

- 对∑-∆调制器以及相关的基本概念、基本理论进行相关研究,逐渐了解描述该种调制器的各项性能指标,明确选取标准,针对具体结构,明确改善方向。

- 对于∑-∆调制器内部的反馈DAC进行了解,对数模转换器所需要注意的指标进行研究,了解在该调制器中反馈数模转换器所面临的问题,针对解决问题所采用的数字校准技术进行研究。

- 在cadence中针对所设计的动态匹配技术进行电路设计,核心内容包括DEM模块以及DAC模块

- 针对所采用的数字校准技术在MATLAB中进行整体仿真,计算参考指标,并对结果进行对比与分析。

第二章 ∑-∆模数转换器原理及结构

本章主要介绍一下∑-∆模数转换器的工作原理、相关的基本理念,基本结构以及有关的性能指标等。

2.1 Σ-∆模数转换器的基本概念及工作原理

在整个模数转换器当中,有几个较为重要的概念需要明确:①量化噪声;②过采样率;③信噪比。本节主要针对这几个概念进行解释。

2.1.1 量化噪声

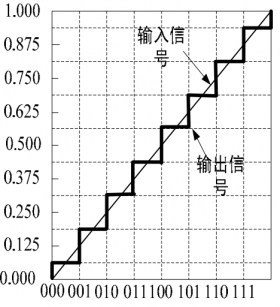

现在科技水平下要将模拟信号转变成数字信号需要三个步骤:抽样、量化以及编码。而模数转换器的作用就在于完成抽样和量化这两个步骤。所谓抽样,是指通过使用每隔一定时间的信号样品值序列来代替原来在时间上连续的信号,也就是使得模拟信号在时间上实现离散化的目的。而量化的作用则是通过使用有限个数的幅度值,将原来连续变化的幅度值实现近似化,即将模拟信号在幅值上实现离散化的目的[10][21][22]。量化过程的误差e(n)指的就是量化前后的数值的差量(如图2-1所示为一个理想的3位量化器转化图)。我们得到的实际的信号可以看成是量化输出信号与量化误差的和。

图2-1 理想量化器转化图

最终的量化误差的大小主要还是取决于使用者是如何将样品值分级,进而取整的。所分的层级级数越多,也就是量化级之间的差或间隔越小,量化误差也就越小。在一定的前提条件下,量化误差的频率特性在采样频率范围内接近白噪声,因此它还有一个别称为量化噪声。两个相邻的量化电平之间的差值被称为最小比特电压(Voltage of Least Significant Bit),常用来表示。假如量化的误差在±之间,而且接近于平均分布,那么通过计算可以得到,量化误差的均方根值为:

2.1.2 过采样率

过采样率是指在采样频率高出传统的奈奎斯特频率时,采样频率所高出的倍数,常用OSR来表示。过采样的做法对于拓展量化误差的频带有显著的影响,在使用传统奈奎斯特方法采样的时候,量化误差的频带宽度是;而在使用过采样的方法时,量化噪声的功率被分配在一个大的频率范围内,因此量化误差的频带宽度则拓展为(。所以通过使用过采样技术,可以有效地减小量化噪声在信号带内的能量。而由于采用了过采样的技术,使得量化误差在信号频带范围内的均方根值变为:

2.1.3 信噪比

信噪比(signal to noise ratio SNR)指信号的能量和噪声的能量在信号频带内的比值,它是DAC和ADC中一个重要的参数。信噪比的大小通常指示着转换器分辨率的高低,该比值常常通过使用正弦输入的方式来进行测量。采用最大输入信号的均方根值和量化噪声的均方根值的比值来进行表示[7][8]。假如用表达式进行表示的话,则为:

(2.3)

该式是在输入信号是在0和间,正弦信号的直流功率均方根是的情况下得到的。它同样适用于奈奎斯特数模转换器或模数转换器。

假设e(n)为均匀分布在中间一个随机产生的数。

设功率谱密度为E(n),则

(2.4)

(2.5)

公式(2.4)(2.5)联立可得

(2.6)

由于信号频带外的噪声都将被系统的数字滤波器消除掉,因此我们只需要考虑频带内部的噪声,落在信号频带内的噪声如下:

(2.7)

剩余内容已隐藏,请支付后下载全文,论文总字数:27118字

相关图片展示:

该课题毕业论文、开题报告、外文翻译、程序设计、图纸设计等资料可联系客服协助查找;