论文总字数:26516字

摘 要

本论文使用FPGA实现同步序列的产生,同步序列的FPGA实现主要分多个部分,数据产生部分,寄存器部分,滤波器部分,时钟部分。论文的主要工作即为上述部分的实现,包括硬件设计和算法实现。

首先,从理论上介绍同步序列产生的算法,主要包括扩频提速插值的思想以及作用,滤波器的性质,以及根升余弦滤波器的选择和属性要求。

其次,描述了同步序列Verilog语言硬件实现的各个子模块,包括源代码和详细解释,还包括了程序下载到开发板的详细说明。

最后,给出了同步序列产生的仿真结果和数据测试结果,并简单介绍了测试方法,对结果进行了分析。

关键词: FPGA实现,Verilog HDL语言,同步序列,扩频,提速插值,资源分配

FPGA Hardware Implementation of synchronization Sequence

Abstract

In this thesis, synchronization sequences are generated with FPGA. Its implementation includes several parts, such as data generation, registers, filters and clocks. The main work of the thesis is listed above, including hardware design and algorithm implementation.

Firstly, algorithms of synchronization sequence generation are provided in theory, which includes spread spectrum interpolation, filter generation as well as root-cosine filter analysis.

Secondly, hardware implementation of sub-modules using Verilog language, such as source codes and detailed explanations, is described. The procedure of downloading program to developing board is also given.

Last, simulation and data test results of synchronization sequences are provided. Test method is briefly described and the final results are analyzed.

Keywords: The FPGA implementation,Verilog HDL language,Synchronization sequence,Spread spectrum,The allocation of resources

目录

摘要………………………………………………………………………………………………………………………….1

Abstract………………………………………………………………………………………………………………….…1

目录……………………………………………………………………………………………………………………….…2

第一章 绪 论

1.1 引言…………………………………………………………………………………………………….…..…3

1.2通信系统中的同步技术……………………………………………........…………………….....3

1.3 FPGA在数字通信中的应用………………………………………………………………….…….4

1.4 论文主要工作与结构安排…………………………………………………………………………5

第二章 理论介绍

2.1提速插值…………………………………………………………………………………………….………6

2.2匹配滤波器

2.2.1匹配滤波器概述………………………………………………………………………….……8

2.2.2匹配滤波器应用…………………………………………………………………………….…9

2.3根升余弦滤波器……………………………………………..…………………………………………11

2.4定点数……………………………………………………………………………………….………..…….12

第三章 FPGA硬件设计

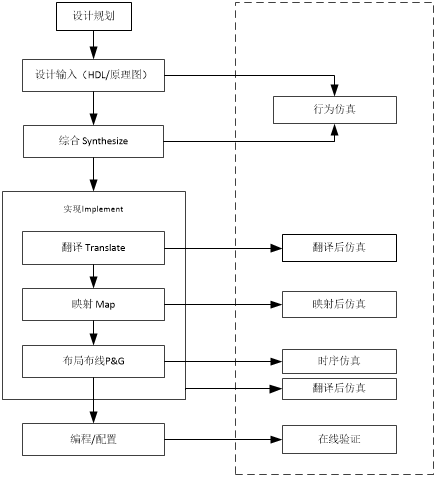

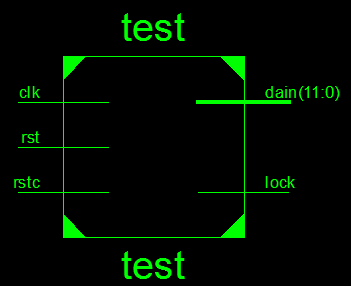

3.1系统总体设计……………………………………………………………………………………….…..14

3.2模块设计详解

3.2.1时钟部分………………………………………………………………………………………….16

3.2.2 数据产生模块…………………………………………………………………………………18

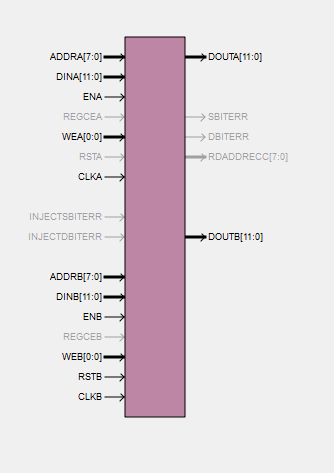

3.2.3 寄存器模块…………………………………………………………………………..…..……18

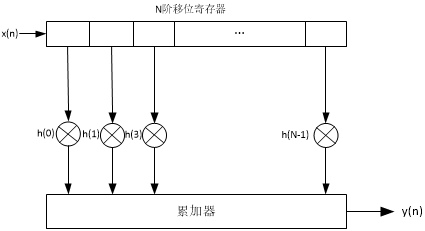

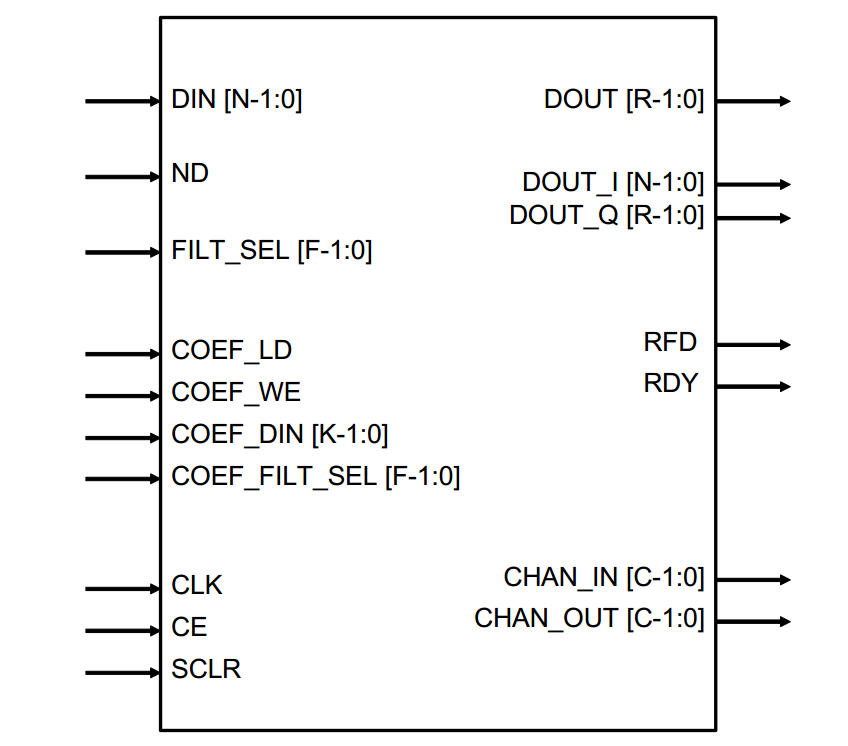

3.2.4 FIR模块……………………………………………………………………………………………20

3.2.5核调用以及配置文件………………………………………………………………………24

第四章 调试与仿真

4.1逻辑分析工具Chipscope…………………………………………………………………………..25

4.2仿真结果…………………………………………………………………………………………...……...26

第五章 总结与展望

5.1工作总结……………………………………………………………………………………………………29

5.2工作展望…………………………………………………………………………………………...………29

参考文献…………………………………………………………………………………………...…………………..30

附录…………………………………………………………………………………………...……………………….....31

- 绪 论

1.1引言

现如今随着人们的生活水平的提高,汽车已经成为每家每户必备的交通工具。据统计,2013年我国的机动车保有量约为1.3个亿,既每十个人就有一辆车,而在十年前的2003年,我国的机动车保有量只有2400万台[1]。在这十年间,我国的汽车数量足足提升了500%还多,而越来越多的汽车也渐渐产生了更多的问题,道路拥挤,交通事故,环境污染等等。每年死于交通事故的人约有6万,改善我们的生活环境已经刻不容缓。

这些年来,通信技术的发展日新月异,其中之一便是自组织网络,自组织网络最早被美国军方于19070年使用,是一种快速而灵活的小范围局域网络。之后于90年代获得了蓬勃的发展,逐渐使用于民生[2-3]。正是由于机动车的数量越来越多而造成的交通状况,车载自组织网络已经成为热点。

车载自网络系统是由附近的车辆组成的网络,其特点为临时而且在动态变化,通过单次信息发送或者多次发送送达目标。车载自组织网络中的每个节点不仅仅是发射端,同时也是接收端和中继站[4-5]。

智能交通系统,主要指将电子传感技术,通信技术,计算机技术,自动化技术等等整合到一起成为一个综合管理系统[6]。它能够实现车辆与车辆,车辆与地面之间的及时交换信息,例如道路的拥挤状况,停车场的车位状况等等,以此为我们带来便利。

车载自组织网是一种新兴的有特点的自组织网络,是智能交通系统的关键组成部分,主要使用于车与车之间或者车与固定设施之间的通信联系。车载自组织网的主要用途是减少交通事故的发生,提高交通运输的效率。车载自组织网中各个节点通过单次传输或者多次传输的方式进行节点间的数据传输,其网络有拓扑结构,具有变化迅速、信道不稳定、容量有限等特点。因此,快速、稳定的同步序列产生和捕获是保障车载自组织网中通信的关键。而当今移动通信技术的发展日新月异,全球一体化的快速进程迫切地需要一个统一的通信系统。而在通信系统当中,同步问题是完成信号正确解调的重要技术之一。同步序列的产生和硬件实现更是当代通信技术的重点。而FPGA可以运用的方面十分广泛,且时序控制能力强,所以选择他来实现这一功能。

1.2通信系统中的同步技术

同步是现今通信系统当中的关键技术之一,其目的在于,能够正确的让发射端和接收端在时间参数上取得同步的数据,以此来安排各自的工作,使收发两端的效率得到提升,并且,只有当收发两端正确的进行同步之后,才可以继续后面的通信操作。整个通信系统的准确性和效率都取决于是否能够快速而精确的进行同步。

在数字通信系统中,接收端需要获知每个码元或者符号的起止时刻,从而后续的设备能够在最佳采样时刻及时对基带的信号进行采样,如果不进行码元同步或者码元同步不正确,就会偏离了最佳采样时刻,这样在解调判决时就会使判决量无法达到最大信噪比,从而造成误码率的增加,之后影响相邻两个码元的正确解调。码元的同步就是要在接收端,产生一次和码元速率相同而且相位对应的时钟脉冲序列,用它来对接收信号开始相关判决。码元同步分为自同步法和外同步法,外同步法的原理是,在原始发送数据中加入额外包含码元定时信息的专用同步信号,之后在接收端提取出来;而自同步法不需要辅助信息,开环自同步法是选择通过对基带接收码元来进行某种非线性的变换后提取码元速率的信息,闭环自同步法更简单,通过比对接收信号的时钟和本地产生的时钟信号,然后将二者之间的定时误差进行记录,闭环反馈至本地时钟再对其进行调整,直到二者正确同步。

然而在无线通信系统中,由于无线信道的不稳定性,以及手法两端的机器设备并非是完美的状态,发送的信号在发送端调制,接收端解调,信道的传播过程中会遇到各种各样的时延,频偏现象,这些现象会对传输的数据造成不确定的影响,如果其数据正好为采样时刻,到达时间,或者相位时,就会对结果产生影响,同步过程的任务就是通过对时间,频率,相位的计算与修改,消除这些由于各种原因产生的误差的影响。

1.3FPGA在数字通信中的应用

现场可编程器件,最早出现于20世纪80年代。它是在PAL、EPLD、CPLD等器件基础上进一步发展而来的新一代逻辑器件。其与专用集成电路(ASIC)相比,具有成本低、设计灵活、开发周期短、可重复配置等优点[7]。

本论文中,我们选择Xilinx FPGA芯片。Xilinx FPGA其最大的优点是在于可重复擦写更改,其内部的结构主要是基于SRAM工艺,一旦断电就易丢失。而且随着工艺的不断提升,FPGA内部所拥有的逻辑门数也越来越多,逻辑单元的密度从上千门到乃至上千万门;I/O管脚也变得更加丰富,并且已经可以支持多种的接口标准;同时其内部还集成了丰富的硬核,如DSP48、RAM、FIR滤波器等。目前对于FPGA开发的主流方法是使用硬件语言(VHDL和Verilog)对电路各个部分的功能进行描述。开发周期和开发成本要缩小很多。

FPGA基于查找表结构,并集成了许多常用的硬核模块。FPGA主要可分为6个模块:可配置逻辑块,嵌入式RAM,输入输出单元,布线资源,时钟资源,还有内嵌的专门硬件电路[8]。通常对于FPGA的配置,通过外部的PROM,其配置方式有许多种,比如从串配置方式、主串配置方式、并行配置方式等。

FPGA具有高集成度、低功耗的特点,如今已经被广泛的应用到通信、汽车电子、以及航空航天等领域[9]。FPGA的发展方向和主要应用可以分为三类:

1.数字信号处理。FPGA内嵌了DSP核以及丰富的各种逻辑资源,使之能够实现许多复杂的数学算法,同时能够快速的对大量数字信号进行处理。

2.逻辑接口设计。FPGA支持高速接口通信协议,并能完成高速的数据收发和可靠的数据传输。

3.SOC,系统芯片。利用FPGA内部资源实现一个虚拟处理器,或者内嵌一个处理器,然后在上面进行嵌入式软件开发。

现代数字通信系统已经向着高速、高带宽、小型化、智能化的方向发展。LTE等第四代无线通信技术对于吞吐量和数据处理速率的各项要求远远高于第三代无线通信系统,而且例如Turbo、LDPC编解码等数字信号处理、快速傅里叶变换/逆变换以及数字预失真等前端的计算也需要大量的数据处理能力。 FPGA具有大量的逻辑单元、丰富的接口和内嵌的硬核资源,能够并行处理大量的数据。就是这些特性决定了FPGA在数字基带系统中被广泛的应用。随着工艺的继续提升,FPGA的集成度就一定会越来越高,同时其功能也会越来越强大。越来越多的需求可以用FPGA来实现。

1.4 论文主要工作与结构安排

同步序列的FPGA实现主要分多个部分,数据产生部分,寄存器部分,滤波器部分,时钟部分。本课题主要工作即为上述部分的实现,包括硬件设计和算法实现。论文结构安排如下:

第一章首先从背景说明,同步技术的解释,以及FPGA的介绍入手,对本课题的大环境进行一个简单的描述。

第二章为理论介绍,主要介绍扩频提速插值的思想以及作用,滤波器的性质,以及根升余弦滤波器的选择和属性要求。

第三章主要描述Verilog实现的各个部分,包括源代码和详细解释,同时也会有烧录上开发板的详细说明。

第四章则为仿真结果以及数据验证,对测试方法也会做简单的说明,最后对结果进行了分析。

第二章 理论介绍

2.1提速插值

对离散时间信号最简单的插值方法就是插零,首先要了解插零后信号频谱的变化。所谓插零,就是对信号x(n)的两个采样点之间插入L-1个零,这样,此时采样频率提高了L倍,即得到新的采样周期T’,

即

(2.1)

新的采样频率为

(2.2)

在x(n)的每一对采样点之间插入L-1个零值,得到

剩余内容已隐藏,请支付后下载全文,论文总字数:26516字

相关图片展示:

该课题毕业论文、开题报告、外文翻译、程序设计、图纸设计等资料可联系客服协助查找;