基于FPGA的简易逻辑分析仪毕业论文

2020-04-09 15:44:53

摘 要

逻辑分析仪是一种类似于示波器,用来分析测量数字系统的逻辑波形和逻辑关系的仪器设备。它的特点是多通道,一次可以得到数以百计的数据。它会实时用逻辑 1(高电平)或逻辑0(低电平)来表示收集的电压,只用考虑测量信号的时间。我们可以在设计电路时用它来检测错误,并找出这些错误的位置。逻辑分析仪就是一个多通道逻辑信号或逻辑数据采样、显示与分析的电子设备。可以将数字系统中的各种信号进行采集后再存储分析。因此在数字系统中,逻辑分析仪有很大的作用。

本文设计了一个简易的8通道的逻辑分析仪,实现对输入的8路逻辑信号进行数据判断、数据存储、采集和处理,然后输出显示的功能。

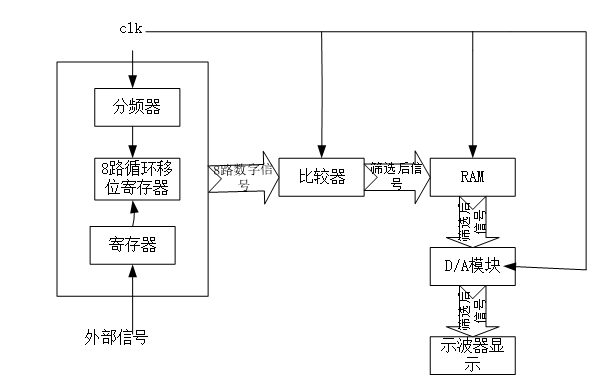

本次设计使用FPGA(现场可编程逻辑门阵列)芯片和VHDL硬件描述语言作为主要设计方法实现8路简易逻辑分析仪。本系统根据逻辑分析仪所要实现的各项功能分别编程设计了对应的功能模块,分别是触发模块,数据缓存模块,分频模块以及存储器模块,并分别进行了仿真验证,在此基础上,完成了系统电路的设计与仿真。

关键词:逻辑分析仪;数据采集;FPGA;VHDL

Abstract

A logical analyzer is an instrument similar to an oscilloscope used to analyze and measure the logical waveform and logical relationship of a digital system. It features multiple channels, with hundreds of data available at a time. It represents the collected voltage in real time with logic 1(high level) or logic 0(low level), and only takes into account the time taken to measure the signal. We can use it to detect errors and find out where they are when designing a circuit. A logical analyzer is an electronic device for sampling, displaying and analyzing logic signals or logical data. Various signals in the digital system can be collected and then stored for analysis. Therefore, in the digital system, the logic analyzer plays a very important role.

In this paper, a simple 8-channel logic analyzer is designed to realize the function of data judgment, data storage, data collection and processing of the input 8-channel logic signals, and then output the display.

This design USES FPGA (field programmable logic gate array) chip and VHDL hardware description language as the main design method to realize 8-channel simple logic analyzer. This system based on logic analyzer in order to realize the functions of programming design, respectively, the corresponding functional modules, respectively is trigger module, data caching module, frequency division module and memory module, and the simulation verification, on this basis, completed the system design and simulation of the circuit.

Key words: Logical analyzer;Data acquisition;FPGA;VHDL

目录

第1章 绪论 1

1.1 研究现状 1

1.2 研究背景及意义 2

1.3 研究内容与章节安排 2

第2章 系统相关技术 3

2.1 设计要求 3

2.2 EDA技术及其发展 3

2.2.1 FPGA简介 4

2.2.2 QuartusII简介 4

2.2.3 硬件描述语言VHDL 5

2.3 总体设计方案 6

2.4 本章小结 9

第 3 章 系统设计 10

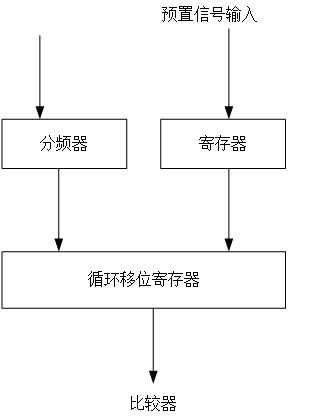

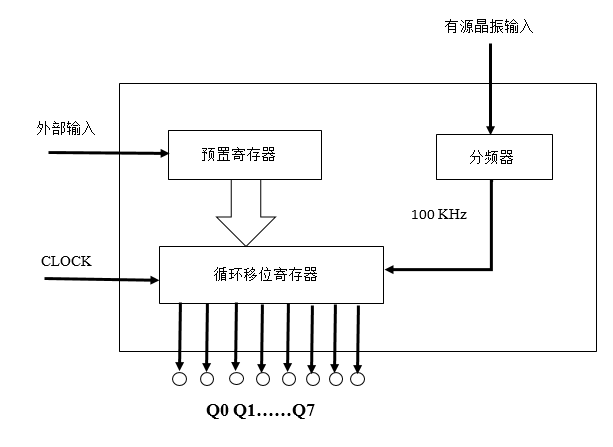

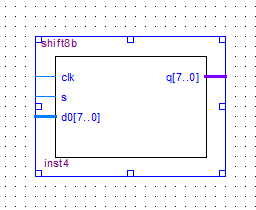

3.1 8位移位数字发生器 10

3.1.1 方案论证 10

3.1.2 数字信号发生器的工作流程图和组成框图 10

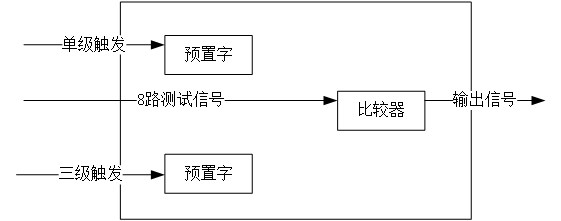

3.2 简易逻辑分析仪 11

3.2.1 方案论证 11

3.2.2逻辑分析仪的工作流程图和组成框图 12

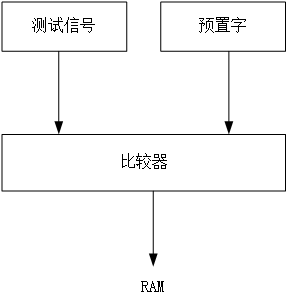

3.3 RAM随机存储器 13

3.3.1 功能分析 13

3.3.2 RAM的实现 13

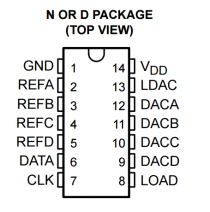

3.4 D/A转换模块 14

3.4.1 D/A 转换器工作原理 14

3.4.2 TLC5620 工作原理 14

3.5本章小结 15

第 4 章 仿真波形 16

4.1 8位移位数字发生器 16

4.1.1 元器件图 16

4.1.2 仿真图 16

4.2 逻辑分析仪的比较器模块 16

4.2.1 元器件图 17

4.2.2 仿真图 17

4.3 RAM随机存储器 17

4.3.1 元器件图 17

4.3.2 仿真图 18

4.4 D/A转换模块 18

4.5 系统顶层的实现和仿真 19

4.6 本章小结 20

第5章 实物测试 21

5.1 DE1-SOC开发板 21

5.2 实物测试 22

第 6章 总结 23

参考文献 24

附录 25

致谢 32

第1章 绪论

1.1 研究现状

一直以来,示波器一直是电路调试的首选仪器,但是随着电路设计的逐渐复杂,尤其是数字设计复杂性增加。工程师认为需要有更适合测试数字电路的仪器。二十世纪七十年代初诞生了世界上第一台逻辑分析仪——许多人都认为这是发现和解决数字设计异常问题的最有效的方法。

逻辑分析仪经过长时间的发展已经历了四代:第一代逻辑分析仪分为定时分析仪和逻辑分析仪,结构比较简单,功能也比较单一,仅具有触发功能和显示方式,运行速度较慢;第二代逻辑分析仪的标志是微机化,定时功能和状态分析的功能被整合到同一台仪器,并且改进了触发和显示的功能,有利于软件和硬件的结合使用;第三代逻辑分析仪有很强的分析能力,尤其善于辨别系统性能,具有通道数多、速度高、存储容量大等优点;第四代产品以一体化为标志,性能相当完善。集成度也有了很大提升 [1]。

逻辑分析仪因为它强大的功能和简易的操作性,在当今社会有着越来越重要的作用,因此也有着很好的市场前景,所以鼓励着很多逻辑分析仪厂商不断研发这新的高质量产品,现在的逻辑分析仪有着越来越高的存储深度,采样率也从几百HZ上升到几千HZ,技术的提升带来的是价格的居高不下,因其技术的复杂性,制作的繁琐性,都造成了逻辑分析仪价格的居高不下。在这样的背景下,已经有厂商在试图在性能和价格之间寻找一个平衡,比如台湾的OITEK科技有限公司就推出了一款0LA2032BTM独立台式EasyDebugTM逻辑分析仪,它拥有32的数据通道可同时采集32位的数据,可以存储最大2Mbytes的数据,它的功能强大,可以独立对数字系统进行数据采集数据处理数据分析,而且价格较低,性价比极高,满足大多数数字电路工程师们的需求,这也对老师们教授数字电路,检测数字电路时也起到了极大的便利,会让学生们直观地感受到数字电路的输出变化。随着技术的逐步发展,现在出现了一种新型的卡式逻辑分析仪,但是它是基于电脑接口的。它就属于高性价比的产品,低廉的价格毫不逊色的功能使其慢慢崭露头角,但是它的缺点也很明显,它是基于电脑插口的,也就是说它只能连接电脑使用,这就造成了很多麻烦,工程师们在一堆硬件电路中很容易被搞得晕头转向。但是时代会不断发展,技术也是不断进步的,我们有理由相信逻辑分析仪的功能会不断拓展,而价格也最终会变得更容易被工程师们接受。就像今天的示波器一样。示波器更多的用在检查模拟电路的信号输出。对于数字电路显得有点力不从心。而逻辑分析仪是一种检查数字电路,排查数字电路故障的仪器,他们功能互补。也许未来会出现一种机器可以将示波器和逻辑分析仪的功能融合,它可以既用来检测模拟电路也可以用来检查数字电路,随着社会的不断发展,技术的不断进步,也许这种仪器在不久的将来就会出现。

1.2 研究背景及意义

逻辑分析仪(Logic Analyzer)就是一个多通道逻辑信号或逻辑数据采样、显示与分析的电子设备。逻辑分析仪可以将数字信号中的脉冲信号、逻辑控制信号、总线数据采集到RAM随机存储器暂存,以备分析和显示。在当今电路设计中示波器仍然占据主流地位,但因为数字电路的飞速发展,越来越多的数字电路设计出现,示波器只能对模拟电路电路的错误分析产生作用。示波器对数字电路的检测显得力不从心。而逻辑分析仪便是一个对数字电路进行时域分析的设备。在测试数字电路,计算机的设计开发和研究,维护各种数字仪器方面起着非常重要的作用。逻辑分析仪作为数字电路设计中不可缺少的测试工具,正在不断崭露头角,逻辑分析仪在多通道、大存储量、高采样速率、多触发功能方面得到更快的发展,在航天、军事、通信等数字系统领域得到越来越广泛的应用[2]。逻辑分析仪强大的功能,在数字电路测试中表现出的高效性,越来越得到广大电路设计工程师们的认可。

但是虽然数字设计师认识到逻辑分析仪在数字电路调试上的有效性,却仍有许多人并未使用逻辑分析仪。HP公司近年来对这一问题进行了深人的市场调查,发现有大部分数字设计师很少使用甚至不使用逻辑分析仪,逻辑分析仪几乎全为部门所有,由许多人共用。特别是在有许多工程师的大公司中,共用逻辑分析仪之后,使其有效性受到很大程度的限制。HP公司的市场调查证实了业界观察家的观点:逻辑分析仪的难于使用和高昂的价格使设计师不能使用逻辑分析仪。

逻辑分析仪虽然以其独特的功能的在数字电路设计中发挥着越来越不可忽视的作用,然而其高昂的价格又不是普通工程师可以负担的起的,所以在日常生产生活中,并不常见到逻辑分析仪的踪影。本文通过设计一个简易的逻辑分析仪,来一探逻辑分析仪的具体功能和在数字电路中逻辑分析仪究竟起到了什么作用。

1.3 研究内容与章节安排

本文设计的逻辑分析仪研究内容与章节安排如下:

第 1 章:简要介绍了逻辑分析仪研究现状和研究意义,介绍了逻辑分析仪现状和未来的发展趋势,阐述了为什么要做这个课题。

第 2 章:介绍了设计逻辑分析仪系统所需要的相关技术,介绍逻辑分析仪的整体模块,分析了逻辑分析仪的功能需求,并介绍了各个模块的具体作用。 分析对比并最终决定了实现方案。

第 3 章:介绍了各个模块的设计方案,包括方案对比和工作框图,详细讲述了各个模块的具体实现和实际作用。

第 4 章:详细介绍了各个模块通过VHDL编程后生成的元器件图。详细介绍了生成的元器件图的使用方法,并对各模块进行仿真后进行连接成顶层实体。

第5章:演示了具体实物的实现过程。将各模块组合之后在硬件电路上的最终实现。

第2章 系统相关技术

2.1 设计要求

本文基于FPGA设计一个8通道的简易逻辑分析仪。本毕业设计要求基于FPGA芯片5CSEMA5F31C6设计8路移位数字信号发生器和逻辑分析仪,要求设计单级触发字采集8路逻辑信号,用示波器显示采集的波形及可移动时间标志线及其所对应的逻辑状态,具备三级逻辑状态触发功能且触发位置可调。

2.2 EDA技术及其发展

EDA即电子设计自动化,是指使用计算机自动完成电子系统的设计[3]。电子设计自动化技术通过电子计算机辅助设计,将电路设计师从硬件电路中解放出来,在计算机中,电路设计师便可以完成数字系统的逻辑综合、设计仿真等工作。EDA技术的发展共经历了以下三个阶段[4]:

- 最初阶段:CAD阶段。因为二十世纪中期mos工艺的广泛应用,可编程逻辑技术以及器件出现,但是由于这是计算机技术本身的不成熟,计算能力有限,计算速度较低,用计算机所做的工作有限,只能起到一些辅助作用,没能在电路设计中起到至关重要的作用,所以也没有引起工程师们的重视。二十世纪八十年代初,EDA及技术发展迅速,出现了一些可以编辑电路图的EDA软件。但这些软件功能单一,每项工作只能由专门的软件对应,操作繁琐,不利于电路的设计,加重了工程师们的工作负担。因此此时的EDA软件并没有大规模普及,但作为新兴的技术,引起了一些研发工程师的兴趣。

- CAE阶段。二十世纪八十年代后,由于计算机技术的发展迅速,计算能力显著提高,计算速度加快,原本的EDA软件也进一步整合,这些集合统一为一个CAE系统。单一软件只能做一项工作的时代过去。使用CAE系统可以自行设计一个电路系统。但这时的CAE系统仍然不够完善,只能做简单的电路设计,对大型系统就显得力不从心。

- EDA阶段。二十世纪九十年代以来,微电子的高速发展,带动了集成电路的发展,集成电路的规模有了质的飞跃。这为制造出高集成芯片的出现提供了条件。也对EDA技术的发展提出了要求。此阶段出现了第三代的EDA技术,以高级语言描述、系统仿真和综合技术为特征[5]。使电路设计不在为硬件而困扰,可以只专注于软件编程,极大提高了系统的设计效率。

目前EDA技术的主要特征:

- 高层综合,通过综合算法,以具体的工艺背景实现高层目标所规定的优化设计。

- 硬件描述语言,比如VHDL和Verilog HDL。

- 平面规划技术(Floorplaning)对逻辑综合和物理版图设计的联合管理。

- 硬件可测试性。

- 软硬件共同处理工具。

- 多线程处理。

EDA技术的设计特点:

- 强大的系统建模与电路仿真功能。

- 采用硬件描述语言进行设计。

- 开发技术的标准化、规范化以及IP核的可利用性。

- 对设计者的硬件知识和硬件经验要求低。

2.2.1 FPGA简介

FPGA(Field-Programmable Gate Array),即现场可编程门阵列[6]。可编程器件不断发展,不断改进,目前FPGA是市场上最受欢迎的可编程器件。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA是特殊的ASIC芯片,除了具有ASIC的特点之外[7],还具有几个优点:

- 芯片容量大,随着集成电路技术的不断发展,芯片规模不断提高,所能实现功能不断提高,还可以实现系统集成。

- 质量可靠。不需要设计人员承担设计风险,投入较少,节省了大量成本。

- 可重复使用,用户可反复擦除使用,在硬件电路不改变的前提下,可以用不同的软件实现不同的功能。

因为其可重复使用特性,使之有很大的容错性,当电路完成设计之后,可以先在FPGA进行实验,来完成电路的测试功能。也正是因为FPGA的出现,使广大设计师不在为硬件电路测试而手忙脚乱。一个出厂后的成品FPGA的逻辑块和连接可以按照设计者而改变,所以FPGA可以方便快捷地完成所需要的逻辑功能。在FPGA上先行测试已经逐渐成为当今电路设计的主流。也正是因为FPGA这种独特的性质使之越来越受到广大工程师们的欢迎。

本次设计采用FPGA的设计方法主要考虑到FPGA的高灵活性,可更改性特点。在设计过程中遇到问题时,能够及时方便的更改程序进行调整,充分发挥了FPGA开发方法的优越性。

2.2.2 QuartusII简介

QuartusII是ALTERA公司提供的EDA设计工具,是当今业界最优秀的EDA设计工具之一,该工具软件为ALTERA公司的器件能达到最高性能和集成度提供了保证。

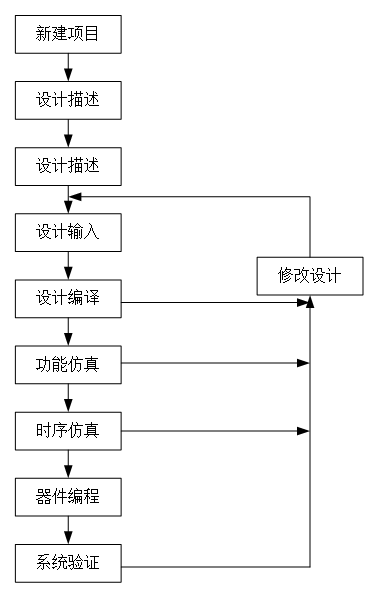

QuartusII是基于项目的EDA设计平台,使用QuartusII软件进行数字电路设计的过程包括新建项目、设计描述、设计输入、设计编译、功能仿真验证、时序仿真验证、器件编程和系统验证等几个步骤,如图1.1所示。其中前六个步骤不需要硬件支持,在一台计算机上即可完成。如果在设计过程的任何一步发现设计缺陷,都可以很方便的修改,重新进行编译仿真。通过时序仿真验证,设计者能发现许多在硬件上难以发现的问题,极大的提高了产品的可靠性。

图2.1 Quartus II设计过程

2.2.3 硬件描述语言VHDL

超高速集成电路硬件描述语言即VHDL,于1983年有美国国防部(DOD)发起创建,由IEEE进一步发展并在1987年作为“IEEE 标准1076”发布[8]。从此,VHDL成为硬件描述语言的业界标准之一。自VHDL出世以后,迅速受到EDA软件厂商和电路设计工程师的追捧,EDA软件厂商们纷纷推出了自己的VHDL设计环境,或者可以兼容VHDL环境,而越来越多的电路工程师们选择VHDL语言来做开发。此后 VHDL在电路设计领域的作用越来越不容易被忽视,并逐步取代了原有的非标准硬件描述语言。1993年,IEEE对VHDL进行了修订,发布了VHDL语言的新版本,进一步优化了VHDL语言,从更高的抽象层次和系统描述能力上扩展VHDL的内容,VHDL语言因其便利性,受到广大工程师们的追捧,再加上很多EDA软件厂商对它的支持,现在已经是市场上最具竞争力的开发工具。有专家认为,在新的世纪中,VHDL语言将承担起大部分的数字系统设计任务。除了作为电子系统设计的主选硬件描述语言外,VHDL在EDA领域的仿真测试、程序模块的移植、ASIC设计源程序的交付、IP核(Intelligence Property core)的应用方面担任着不可或缺的角色,因此不可避免地将成为了必要的设计开发工具。

VHDL作为一种硬件编程语言,是连接硬件和软件的工具,所以虽然语法形式很像一般的计算机高级语言,但是却含有很多硬件特征的语句。VHDL进行设计时,会先设计实体,实体的工作就是定义各个端口,明确各个端口的作用,然后使用端口和其他模块连接并与其他模块通信,然后设计结构体,结构体是模块的具体功能的决定者。也是VHDL设计程序的主体部分,正是这部分的设计才决定了VHDL整体程序的功能。

以上是毕业论文大纲或资料介绍,该课题完整毕业论文、开题报告、任务书、程序设计、图纸设计等资料请添加微信获取,微信号:bysjorg。

相关图片展示:

课题毕业论文、开题报告、任务书、外文翻译、程序设计、图纸设计等资料可联系客服协助查找。